# **Variorum Documentation**

Release 0.7.0

LLNS

Mar 26, 2024

# BASICS

| 1 | Variorum Project Resources                              | 3    |

|---|---------------------------------------------------------|------|

| 2 | Lead Developers                                         | 5    |

| 3 | Code Of Conduct                                         | 7    |

| 4 | Acknowledgments                                         | 9    |

| 5 |                                                         | 11   |

|   | 5.1 Quick Start Guide                                   |      |

|   | 5.2 Building Variorum                                   |      |

|   | 5.3 Variorum Overview                                   |      |

|   | 5.4 Variorum API                                        |      |

|   | 1 0                                                     |      |

|   | <ul> <li>5.6 Supported Platform Documentation</li></ul> |      |

|   | 5.8 Variorum Utilities                                  |      |

|   | 5.9 Variorum Print Functions                            |      |

|   | 5.10 Variorum Cap Functions                             |      |

|   | 5.10 Variorum JSON-Support Functions                    |      |

|   | 5.12 Variorum Enable/Disable Functions                  |      |

|   | 5.12 Variorum Topology Functions                        |      |

|   | 5.14 JSON API                                           |      |

|   | 5.15 Contributing Guide                                 |      |

|   | 5.16 Variorum Developer Documentation                   |      |

|   | 5.17 Variorum Unit Tests                                |      |

|   | 5.18 Integrating with Variorum                          |      |

|   | 5.19 ECP Argo Project                                   |      |

|   | 5.20 HPC PowerStack Initiative                          |      |

|   | 5.21 Publications and Presentations                     |      |

|   | 5.22 Contributors                                       | . 81 |

|   | 5.23 Contributor Covenant Code of Conduct               |      |

|   | 5.24 Releases                                           |      |

|   | 5.25 License Info                                       |      |

| 6 | Indices and tables                                      | 87   |

#### Index

i

89

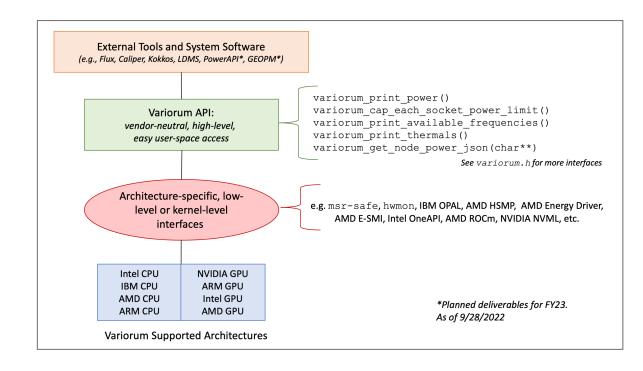

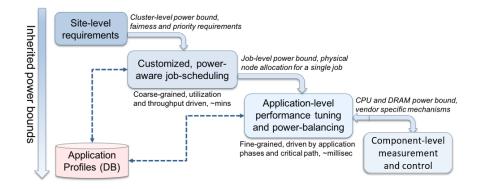

Variorum is an extensible, vendor-neutral library for exposing power and performance capabilities of low-level hardware dials across diverse architectures in a user-friendly manner. It is part of the *ECP Argo Project*, and is a key component for node-level power management in the *HPC PowerStack Initiative*. Variorum provides vendor-neutral APIs such that the user can query or control hardware dials without needing to know the underlying vendor's implementation (for example, model-specific registers or sensor interfaces). These APIs enable application developers to gain a better understanding of power, energy, and performance through various metrics. Additionally, the APIs may enable system software to control hardware dials to optimize for a particular goal. Variorum focuses on ease of use and reduced integration burden in applications, which it accomplishes by providing:

- Examples which demonstrate how to use Variorum in a stand-alone program.

- A performance analysis sampler that runs alongside the application.

- A JSON API to allow integration with higher-level system software, such as job schedulers, distributed monitoring frameworks, or application-level runtime systems.

# ONE

# **VARIORUM PROJECT RESOURCES**

Online Documentation https://variorum.readthedocs.io/ Github Source Repo http://github.com/llnl/variorum Issue Tracker http://github.com/llnl/variorum/issues

# TWO

# LEAD DEVELOPERS

- Stephanie Brink (LLNL)

- Aniruddha Marathe (LLNL)

- Tapasya Patki (LLNL)

- Barry Rountree (LLNL)

- Kathleen Shoga (LLNL)

# THREE

# CODE OF CONDUCT

See Contributor Covenant Code of Conduct.

# FOUR

# ACKNOWLEDGMENTS

This research was supported by the Exascale Computing Project (17-SC-20-SC), a joint project of the U.S. Department of Energy's Office of Science and National Nuclear Security Administration, responsible for delivering a capable exascale ecosystem, including software, applications, and hardware technology, to support the nation's exascale computing imperative.

# VARIORUM DOCUMENTATION

# 5.1 Quick Start Guide

The simplest way to install Variorum is using the default CMake settings. Building Variorum requires the hwloc and jansson libraries. The default build targets the Intel platform and assumes msr-safe kernel module access.

```

# install hwloc and jansson dependencies

sudo apt-get install libhwloc15 libhwloc-dev libjansson4 libjansson-dev

git clone https://github.com/LLNL/variorum.git

cd variorum

mkdir build install

cd build

cmake -DCMAKE_INSTALL_PREFIX=../install ../src

make -j8

make install

```

Note that HWLOC\_DIR and JANSSON\_DIR may need to be set correctly if installing from scratch. Variorum also supports host-config files, which make the build process easier by setting all necessary paths in one place. Details on using host configuration files can be found here.

Please ensure that the dependencies for each platform are met before building Variorum. These include the kernel module msr-safe for Intel systems, msr, amd\_energy\_driver and HSMP driver for AMD sytems, OPAL firmware and sensors for IBM, and NVML for NVIDIA. Details of each of these can be found in the respective vendor pages, see *Supported Platform Documentation*.

For more details about building and installing Variorum, see *Building Variorum*, which provides detailed information about building Variorum for specific hosts, Variorum's other CMake options and installing with spack.

Function-level descriptions of Variorum's APIs as well as the architectures that have implementations in Variorum are provided in the following sections:

- Variorum Print Functions

- Variorum Cap Functions

- Variorum JSON-Support Functions

- Variorum Enable/Disable Functions

- Variorum Topology Functions

- JSON API

For beginners, the ECP Variorum Lecture Series is beneficial.

# 5.2 Building Variorum

Variorum can be built from source with CMake or with spack. Building Variorum creates the libvariorum library, the var\_monitor monitoring tool, and Variorum examples.

#### 5.2.1 Build Dependencies

The build dependencies for a **minimal build** with no parallel components require the following:

- C

- hwloc

- jansson

- Access to vendor-specific drivers or modules (see Supported Platform Documentation).

For a parallel build with MPI/OpenMP, Variorum depends on:

• rankstr (only required for MPI/OpenMP builds)

The CMake variables (ENABLE\_MPI={ON,OFF} and ENABLE\_OPENMP={ON,OFF}) control the building of parallel examples. If ENABLE\_MPI=ON, an MPI compiler is required.

#### hwloc (Required)

hwloc is an open-source project providing a portable abstraction of the hierarchical topology of modern architectures.

Variorum leverages hwloc for detecting hardware topology. When reading/writing a register on a particular hardware thread, hwloc can map that to the correct physical socket.

#### jansson (Required)

jansson is an open-source C library for encoding, decoding and manipulating JSON data.

Variorum leverages JANSSON to provide a JSON-based API that can retrieve power data for external tools/software.

#### rankstr (Optional)

rankstr is an open-source C library providing functions that identify unique strings across an MPI communicator.

Variorum leverages rankstr to split a communicator into subcommunicators by hostname. The allows for a single control or monitor process in Variorum to for example, enforce a power or frequency limit on a node or to print the hardware counters once on a node.

#### 5.2.2 Building with CMake

Variorum can be built and installed as follows after cloning from GitHub:

```

# install hwloc and jansson dependencies

sudo apt-get install libhwloc15 libhwloc-dev libjansson4 libjansson-dev

git clone https://github.com/llnl/variorum

cd variorum

mkdir build install

cd build

cmake -DCMAKE_INSTALL_PREFIX=../install ../src

make -j8

make install

```

### 5.2.3 Host Config Files

To handle build options, third party library paths, etc., we rely on CMake's initial-cache file mechanism. We call these initial-cache files host-config files, as we typically create a file for each platform or specific hosts if necessary. These can be passed to CMake via the -C command line option as shown below:

cmake {other options} -C .../host-configs/{config\_file}.cmake .../src

An example is provided in host-configs/boilerplate.cmake to create your own configuration file. Example configuration files named by machine hostname, the SYS\_TYPE environment variable, and platform name (via uname) are also provided in the host-configs directory. These files use standard CMake commands. CMake set commands need to specify the root cache path as follows:

set(CMAKE\_VARIABLE\_NAME {VALUE} CACHE PATH "")

#### 5.2.4 CMake Build Options

Variorum's build system supports the following CMake options:

- HWLOC\_DIR Path to an HWLOC install.

- JANSSON\_DIR Path to a JANSSON install.

- SPHINX\_EXECUTABLE Path to sphinx-build binary (required for documentation).

- VARIORUM\_WITH\_AMD\_CPU (default=OFF) Enable Variorum build for AMD CPU architecture.

- VARIORUM\_WITH\_NVIDIA\_GPU (default=OFF) Enable Variorum build for Nvidia GPU architecture.

- VARIORUM\_WITH\_IBM\_CPU (default=OFF) Enable Variorum build for IBM CPU architecture.

- VARIORUM\_WITH\_ARM\_CPU (default=OFF) Enable Variorum build for ARM CPU architecture.

- VARIORUM\_WITH\_INTEL\_CPU (default=ON) Enable Variorum build for Intel CPU architecture.

- VARIORUM\_WITH\_INTEL\_GPU (default=OFF) Enable Variorum build for Intel discrete GPU architecture.

- ENABLE\_FORTRAN (default=ON) Enable Fortran compiler for building example integration with Fortran application, Fortran compiler must exist.

- ENABLE\_PYTHON (default=ON) Enable Python wrappers for adding PyVariorum examples.

- ENABLE\_MPI (default=OFF) Enable MPI compiler for building MPI examples, MPI compiler must exist.

- ENABLE\_OPENMP (default=ON) Enable OpenMP extensions for building OpenMP examples.

- ENABLE\_WARNINGS (default=OFF) Build with compiler warning flags Wall Wextra Werror, used primarily by developers.

- BUILD\_DOCS (default=ON) Controls if the Variorum documentation is built (when sphinx and doxygen are found).

- BUILD\_SHARED\_LIBS (default=ON) Controls if shared (ON) or static (OFF) libraries are built.

- BUILD\_TESTS (default=ON) Controls if unit tests are built.

- VARIORUM\_DEBUG (default=OFF) Enable Variorum debug statements, useful if values are not translating correctly.

- USE\_MSR\_SAFE\_BEFORE\_1\_5\_0 (default=OFF) Use msr-safe prior to v1.5.0, dependency of Intel architectures for accessing counters from userspace.

#### 5.2.5 Building on Multiple Architectures

Several HPC systems have compute nodes that are composed of components or hardware from different vendors. An example is the Sierra supercomputer at LLNL, where the CPUs are based on IBM platform (Power9), and the GPUs are from NVIDIA (Volta). Because power and energy dials are vendor-specific, we need to enable a *multi-architecture* build for such platforms. As of version 0.7, we have added support for such builds within Variorum. These can now be specified with turning the CMake options for the associated devices, for example. VARIORUM\_WITH\_NVIDIA\_GPU and VARIORUM\_WITH\_IBM\_CPU can both be set to ON during the same build.

Support for multi-architecture builds is still new and limited, especially with the JSON-based APIs. We are working toward adding more features in the near future.

#### 5.2.6 Building with Spack

To install Variorum with all options (and also build all of its dependencies as necessary) run:

spack install variorum

The Variorum spack package provides several variants that customize the options and dependencies used to build Variorum (see table below). Variants are enabled using + and disabled using ~.

| Variant    | Description                                   | Default                                      |               |      |  |

|------------|-----------------------------------------------|----------------------------------------------|---------------|------|--|

| shared     | Build Variorum as shared library              | ON (+shared)                                 |               |      |  |

| docs       | Build Variorum's Documentation                | OFF (~docs)                                  |               |      |  |

| log        | Enable Variorum's logging infrastruc-<br>ture | le Variorum's logging infrastruc- OFF (~log) |               |      |  |

| build_type | Specify build type                            | Release with<br>(build_type=RelWithDebugI    | Debug<br>nfo) | Info |  |

### 5.2.7 Debugging

Setting the VARIORUM\_LOG environment variable at runtime to VARIORUM\_LOG=1 will print out debugging information.

# 5.3 Variorum Overview

Variorum is a production-grade software infrastructure for exposing low-level control and monitoring of a system's underlying hardware features, with a focus on power, energy and thermal dials. It is a significant evolution based on an older open-source library developed at LLNL, called libmsr. Variorum is vendor-neutral, and can easily be ported to different hardware devices, as well as different generations within a particular device. More specifically, Variorum's flexible design supports a set of features that may exist on one generation of hardware, but not on another.

### 5.3.1 Design Principles

To guide the development of Variorum, we focused on a set of important requirements extracted from our learnings with the development of libmsr. Here are Variorum's requirements:

- **Create device-agnostic APIs**: We do not want to require the user to have to know or understand how to interface with each device. The library is built for a target architecture, which may be heterogeneous, and can collect data from each device through a single front-facing interface.

- **Provide a simple interface**: We want users and tool developers to not only collect information from the underlying hardware, but also to have the ability to control various features.

- Ease in extending to new devices and generations within a device: Variorum makes it easy to support new features, deprecate old features among generations of devices, and adapt features that may have different domains of control from one generation to another (i.e., sockets, cores, threads).

# 5.3.2 System Diagram

# 5.4 Variorum API

Variorum supports vendor-neutral power and energy management through its rich API. Please refer to the top-level API, as well as the specific descriptions of the JSON API and the Best Effort Power Capping API. The JSON API allows system software interacting with Variorum to obtain data in a portable, vendor-neutral manner.

### 5.4.1 Top-level API

The top-level API for Variorum is in the variorum.h header file. Function-level descriptions as well as the architectures that have implementations in Variorum are described in the following sections:

- Variorum Print Functions

- Variorum Cap Functions

- Variorum JSON-Support Functions

- Variorum Enable/Disable Functions

- Variorum Topology Functions

- JSON API

### 5.4.2 Variorum Wrappers

As of v0.6.0, Variorum also supports Fortran and Python APIs for Variorum, these can be found in the src/wrappers directory. By default, these wrappers will be enabled. The Fortran wrapper is built and installed if Fortran is found and enabled. For the Python module (called pyVariorum), a pip based install or setting of PYTHONPATH is needed. Please refer to the README in the src/wrappers/python directory for the details. Examples on the usage of these wrappers can be found in the src/examples/fortran-examples and the src/examples/python-examples directories, respectively.

### 5.4.3 **JSON API**

The current JSON API depends on the JANSSON-C library and has a vendor-neutral format. The API has been tested on Intel, IBM and ARM architectures, and can be used to easily integrate with Variorum (see *Integrating with Variorum*).

#### **Obtaining Power Consumption**

The API to obtain node power has the following format. It takes a string (char\*\*) by reference as input, and populates this string with a JSON object with CPU, memory, GPU (when available), and total node power. The total node power is estimated as a summation of available domains if it is not directly reported by the underlying architecture (such as Intel).

The variorum\_get\_node\_power\_json(char\*\*) includes a string type JSON object with the following keys:

- hostname (string value)

- timestamp (integer value)

- power\_node (real value)

- power\_cpu\_watts\_socket\* (real value)

- power\_mem\_watts\_socket\* (real value)

• power\_gpu\_watts\_socket\* (real value)

The "\*" here refers to Socket ID. While more than one socket is supported, our test systems had only 2 sockets. Note that on the IBM Power9 platform, only the first socket (Chip-0) has the PWRSYS sensor, which directly reports total node power. Additionally, both sockets here report CPU, Memory and GPU power.

On Intel microarchitectures, total node power is not reported by hardware. As a result, total node power is estimated by adding CPU and DRAM power on both sockets.

For GPU power, IBM Power9 reports a single value, which is the sum of power consumed by all the GPUs on a particular socket. Our JSON object captures this with a power\_gpu\_socket\_\* interface, and does not report individual GPU power in the JSON object (this data is however available separately without JSON).

On systems without GPUs, or systems without memory power information, the value of the JSON fields is currently set to -1.0 to indicate that the GPU power or memory power cannot be measured directly. This has been done to ensure that the JSON object in itself stays vendor-neutral from a tools perspective. A future extension through NVML integration will allow for this information to report individual GPU power as well as total GPU power per socket with a cross-architectural build, similar to Variorum's variorum\_get\_node\_power() API.

#### **Querying Power Domains**

The API for querying power domains allows users to query Variorum to obtain information about domains that can be measured and controlled on a certain architecture. It also includes information on the units of measurement and control, as well as information on the minimum and maximum values for setting the controls (control\_range). If a certain domain is unsupported, it is marked as such.

The query API, variorum\_get\_node\_power\_domain\_info\_json(char\*\*), accepts a string by reference and includes the following vendor-neutral keys:

- hostname (string value)

- timestamp (integer value)

- measurement (comma-separated string value)

- control (comma-separated string value)

- unsupported (comma-separated string value)

- measurement\_units (comma-separated string value)

- control\_units (comma-separated string value)

- control\_range (comma-separated string value)

#### **Obtaining Node Utilization**

The API to obtain node utilization has the following format. It takes a string (char\*\*) by reference as input, and populates this string with a JSON object with total CPU, system CPU, user CPU, total memory, and GPU (when available) utilizations. It reports the utilization of each available GPU. GPU utilization is obtained using the NVML and RSMI APIs. The total memory utilization is computed using /proc/meminfo, and CPU utilizations is computed using /proc/stat.

The variorum\_get\_utilization\_json(char \*\*get\_util\_obj\_str) function returns a string type nested JSON object. An example is provided below:

```

{

"hostname": {

"CPU": {

```

(continues on next page)

(continued from previous page)

```

"total_util%": (Real),

"user_util%": (Real),

"system_util%": (Real),

},

"memory_util%": (Real),

"timestamp": (Integer),

"GPU": {

"Socket_*": {

"GPUn*#_util%": (Integer)

}

}

}

}

```

The \* here refers to socket ID, and the # refers to GPU ID.

The variorum\_get\_utilization\_json(char \*\*get\_util\_obj\_str) function returns a string type nested JSON object. An example is provided below:

The \* here refers to socket ID, and the # refers to GPU ID.

### 5.4.4 Best Effort Power Capping

We support setting best effort node power limits in a vendor-neutral manner. This interface has been developed from the point of view of higher-level tools that utilize Variorum on diverse architectures and need to make node-level decisions. When the underlying hardware does not directly support a node-level power cap, a best-effort power cap is determined in software to provide an easier interface for higher-level tools (e.g. Flux, Kokkos, etc).

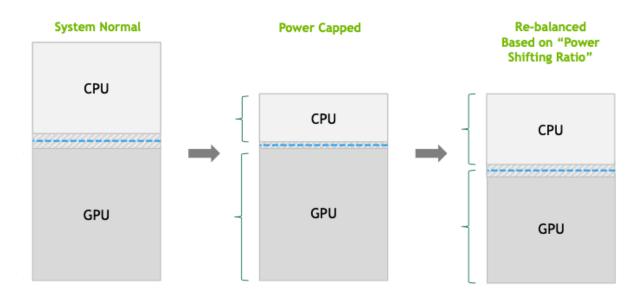

For example, while IBM Witherspoon inherently provides the ability to set a node-level power cap in watts in hardware through its OPAL infrastructure, Intel architectures currently do not support a direct node level power cap through MSRs. Instead, on Intel architectures, fine-grained CPU and DRAM level power caps can be dialed in using MSRs. Note that IBM Witherspoon does not provide fine-grained capping for CPU and DRAM level, but allows for a power-shifting ratio between the CPU and GPU components on a socket (see IBM documentation).

Our API, variorum\_cap\_best\_effort\_node\_power\_limit(), allows us to set a best effort power cap on Intel architectures by taking the input power cap value, and uniformly distributing it across sockets as CPU power caps. Currently, we do not set memory power caps, but we plan to develop better techniques for best-effort software capping in the future.

# 5.5 Example Programs

Variorum provides some examples in the examples/ directory. These include examples of our APIs, usage with MPI and OpenMP, and an example for integrating with Variorum using the JSON API. Note that on Intel systems, we make a call to Variorum print API twice in our examples, as Intel systems require a delta between values to report adequate power numbers.

**Note:** All example codes have a print and print\_verbose version showcasing the different printouts supported by Variorum.

#### 5.5.1 Print Power Limit

The example below gets the power limits of the platform. The print API prints the output in tabular format that can be filtered and parsed by a data analysis framework, such as R or Python.

On an Intel platform, the output of this example should be similar to the following.

\_LOG\_VARIORUM\_ENTER:~/variorum/src/variorum/variorum.c:variorum\_print\_power\_limit::143 \_PACKAGE\_POWER\_LIMITS Offset Host Socket Bits PowerLimit1\_W TimeWindow1\_sec PowerLimit2\_ →W TimeWindow2\_sec \_PACKAGE\_POWER\_LIMITS 0x610 thompson 0 0x7851000158438 135.000000 1.000000 162.000000 0. →007812 \_PACKAGE\_POWER\_LIMITS 0x610 thompson 1 0x7851000158438 135.000000 1.000000 162.000000 0. **→007812** \_DRAM\_POWER\_LIMIT Offset Host Socket Bits PowerLimit\_W TimeWindow\_sec \_DRAM\_POWER\_LIMIT 0x618 thompson 0 0x0 0.000000 0.000977 \_DRAM\_POWER\_LIMIT 0x618 thompson 1 0x0 0.000000 0.000977 \_PACKAGE\_POWER\_INFO Offset Host Socket Bits MaxPower\_W MinPower\_W MaxTimeWindow\_sec\_  $\rightarrow$  ThermPower\_W \_PACKAGE\_POWER\_INFO 0x614 thompson 0 0x2f087001380438 270.000000 39.000000 40.000000 135.  $\rightarrow 000000$ \_PACKAGE\_POWER\_INFO 0x614 thompson 1 0x2f087001380438 270.0000000 39.0000000 40.0000000 135. <u>→000000</u> \_RAPL\_POWER\_UNITS Offset Host Socket Bits PowerUnit\_W EnergyUnit\_J TimeUnit\_sec \_RAPL\_POWER\_UNITS 0x606 thompson 0 0xa0e03 0.125000 0.000061 0.000977 \_RAPL\_POWER\_UNITS 0x606 thompson 1 0xa0e03 0.125000 0.000061 0.000977 \_LOG\_VARIORUM\_EXIT:~/variorum/src/variorum/variorum.c:variorum\_print\_power\_limit::165

On an IBM Power9 platform, the output may look similar to:

\_LOG\_VARIORUM\_ENTER:~/variorum/src/variorum/variorum.c:variorum\_print\_power\_limit::143 \_POWERCAP Host CurrentPower\_W MaxPower\_W MinPower\_W PSR\_CPU\_to\_GPU\_0\_% PSR\_CPU\_to\_GPU\_8\_% \_POWERCAP lassen3 3050 3050 500 100 100 \_LOG\_VARIORUM\_EXIT:~/variorum/src/variorum/variorum.c:variorum\_print\_power\_limit::165 On an Nvidia GPU platform, the output may look similar to:

```

_LOG_VARIORUM_ENTER:~/variorum/src/variorum/variorum.c:variorum_print_power_limit::143

_GPU_POWER_LIMIT Host Socket DeviceID PowerLimit_W

_GPU_POWER_LIMIT lassen1 0 0 300.000

_GPU_POWER_LIMIT lassen1 0 1 300.000

```

(continues on next page)

(continued from previous page)

\_GPU\_POWER\_LIMIT lassen1 1 2 300.000 \_GPU\_POWER\_LIMIT lassen1 1 3 300.000 \_LOG\_VARIORUM\_EXIT:~/variorum/src/variorum/variorum.c:variorum\_print\_power\_limit::165

### 5.5.2 Print Verbose Power Limit

The example below gets the power limits of the platform. The print\_verbose API prints the output in verbose format that is more human-readable (with units, titles, etc.).

```

// Copyright 2019-2023 Lawrence Livermore National Security, LLC and other

// Variorum Project Developers. See the top-level LICENSE file for details.

//

// SPDX-License-Identifier: MIT

#include <getopt.h>

#include <stdio.h>

#include <variorum.h>

int main(int argc, char **argv)

{

int ret;

const char *usage = "Usage: %s [-h] [-v]\n";

int opt:

while ((opt = getopt(argc, argv, "hv")) != -1)

{

switch (opt)

{

case 'h':

printf(usage, argv[0]);

return 0;

case 'v':

printf("%s\n", variorum_get_current_version());

return 0;

default:

fprintf(stderr, usage, argv[0]);

return -1;

}

}

ret = variorum_print_verbose_power_limit();

if (ret != 0)

{

printf("Print verbose power limit failed!\n");

}

return ret;

}

```

On an Intel platform, the output of this example should be similar to the following:

```

_LOG_VARIORUM_ENTER:~/variorum/src/variorum/variorum.c:variorum_print_verbose_power_

\rightarrow limit::180

_PACKAGE_POWER_LIMIT Offset: 0x610, Host: thompson, Socket: 0, Bits: 0x7851000158438,

→PowerLimit1: 135.000000 W, TimeWindow1: 1.0000000 sec, PowerLimit2: 162.000000 W,

→TimeWindow2: 0.007812 sec

_PACKAGE_POWER_LIMIT Offset: 0x610, Host: thompson, Socket: 1, Bits: 0x7851000158438,

→PowerLimit1: 135.000000 W, TimeWindow1: 1.0000000 sec, PowerLimit2: 162.000000 W,

→TimeWindow2: 0.007812 sec

_DRAM_POWER_LIMIT Offset: 0x618, Host: thompson, Socket: 0, Bits: 0x0, PowerLimit: 0.

→000000 W, TimeWindow: 0.000977 sec

_DRAM_POWER_LIMIT Offset: 0x618, Host: thompson, Socket: 1, Bits: 0x0, PowerLimit: 0.

→000000 W, TimeWindow: 0.000977 sec

_PACKAGE_POWER_INFO Offset: 0x614, Host: thompson, Socket: 0, Bits: 0x2f087001380438,

→MaxPower: 270.000000 W, MinPower: 39.000000 W, MaxWindow: 40.000000 sec, ThermPower:

→135.000000 W

_PACKAGE_POWER_INFO Offset: 0x614, Host: thompson, Socket: 1, Bits: 0x2f087001380438,

→MaxPower: 270.000000 W, MinPower: 39.000000 W, MaxTimeWindow: 40.000000 sec,

\rightarrow ThermPower: 135.000000 W

_RAPL_POWER_UNITS Offset: 0x606, Host: thompson, Socket: 0, Bits: 0xa0e03, PowerUnit: 0.

→125000 W, EnergyUnit: 0.000061 J, TimeUnit: 0.000977 sec

_RAPL_POWER_UNITS Offset: 0x606, Host: thompson, Socket: 1, Bits: 0xa0e03, PowerUnit: 0.

→125000 W, EnergyUnit: 0.000061 J, TimeUnit: 0.000977 sec

_LOG_VARIORUM_EXIT:~/variorum/src/variorum/variorum.c:variorum_print_verbose_power_

\rightarrow limit::202

```

On an IBM platform, the output may look similar to:

```

_LOG_VARIORUM_ENTER:~/variorum/src/variorum/variorum.c:variorum_print_verbose_power_

→limit::180

_POWERCAP Host: lassen3, CurrentPower: 3050 W, MaxPower: 3050 W, MinPower: 500 W, PSR_

→CPU_to_GPU_0: 100%, PSR_CPU_to_GPU_8: 100%

_LOG_VARIORUM_EXIT:~/variorum/src/variorum/variorum.c:variorum_print_verbose_power_

→limit::202

```

On an Nvidia platform, the output may look similar to:

```

_LOG_VARIORUM_ENTER:~/variorum/src/variorum/variorum.c:variorum_print_verbose_power_

→limit::180

_GPU_POWER_LIMIT Host: lassen1, Socket: 0, DeviceID: 0, PowerLimit: 300.000 W

_GPU_POWER_LIMIT Host: lassen1, Socket: 0, DeviceID: 1, PowerLimit: 300.000 W

_GPU_POWER_LIMIT Host: lassen1, Socket: 1, DeviceID: 2, PowerLimit: 300.000 W

_GPU_POWER_LIMIT Host: lassen1, Socket: 1, DeviceID: 3, PowerLimit: 300.000 W

_LOG_VARIORUM_EXIT:~/variorum/src/variorum/variorum.c:variorum_print_verbose_power_

→limit::202

```

# 5.6 Supported Platform Documentation

These are the currently supported platforms in Variorum.

### 5.6.1 AMD Overview

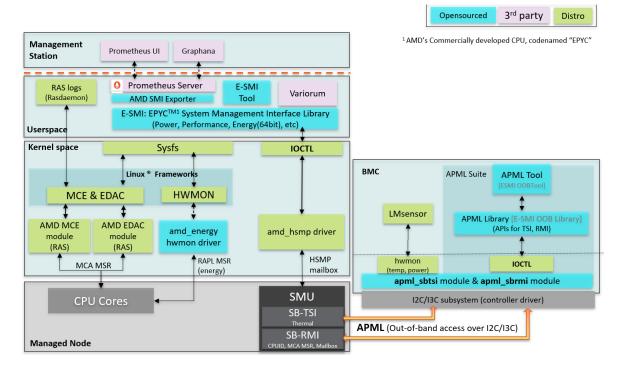

AMD platforms support in-band monitoring and control through sensors and machine-specific registers for CPUs as well as GPUs. AMD provides and open-source stack of its drivers as well as its in-band libraries that Variorum leverages.

#### **Requirements for AMD CPUs**

Beginning with Variorum 0.5.0, AMD processors from the AMD EPYC Milan family 19h, models 0-Fh and 30h-3Fh are supported. The current port is also expected to be supported on the upcoming AMD EPYC Genoa architecture. This functionality has been tested on Linux distributions SLES15 and Ubuntu 18.04. This port depends on the AMD open-sourced software stack components listed below:

- 1. EPYC System Management Interface In-band Library (E-SMI library) available at https://github.com/amd/esmi\_ ib\_library

- 2. AMD Energy Driver https://github.com/amd/amd\_energy

- 3. HSMP driver for power metrics https://github.com/amd/amd\_hsmp

The E-SMI library provides the C API for user space application of the AMD Energy Driver and the AMD HSMP modules.

The AMD Energy Driver is an out-of-tree kernel module that allows for core and socket energy counter access through MSRs and RAPL via hwmon sys entries. These registers are updated every millisecond and cleared on reset of the system. Some registers of interest include:

- Power, Energy and Time Units

- MSR\_RAPL\_POWER\_UNIT/ C001\_0299: shared with all cores in the socket

- Energy consumed by each core

- MSR\_CORE\_ENERGY\_STATUS/ C001\_029A: 32-bitRO, Accumulator, core-level power reporting

- Energy consumed by Socket

- MSR\_PACKAGE\_ENERGY\_STATUS/ C001\_029B: 32-bitRO, Accumulator, socket-level power reporting, shared with all cores in socket

The Host System Management Port (HSMP) kernel module allows for *setting* of power caps, boostlimits and PCIe access. It provides user level access to the HSMP mailboxes implemented by the firmware in the System Management Unit (SMU). AMD Power Control Knobs are exposed through HSMP via sysfs.

- amd\_hsmp/cpuX/: Directory for each possible CPU

- boost\_limit (RW): HSMP boost limit for the core in MHz

- amd\_hsmp/socketX/: Directory for each possible socket

- boost\_limit (WO): Set HSMP boost limit for the socket in MHz

- c0\_residency (RO): Average % all cores are in C0 state

- cclk\_limit (RO): Most restrictive core clock (CCLK) limit in MHz

- fabric\_clocks (RO): Data fabric (FCLK) and memory (MCLK) in MHz

- fabric\_pstate (WO): Set data fabric P-state, -1 for autonomous

- power (RO): Average socket power in milliwatts

- power\_limit (RW): Socket power limit in milliwatts

- power\_limit\_max (RO): Maximum possible value for power limit in mW

- proc\_hot (RO): Socket PROC\_HOT status (1 = active, 0 = inactive)

- tctl (RO): Thermal Control value (not temperature)

We expect a similar software stack to be available on the upcoming El Capitan supercomputer at Lawrence Livermore National Laboratory.

#### **Requirements for AMD GPUs**

Beginning with Variorum 0.6.0, we support AMD Radeon Instinct GPUs with the help of the Radeon Open Compute management (ROCm) stack. The Variorum AMD GPU port currently requires ROCm System Management Interface (ROCm-SMI) v5.2.0, and supports various AMD GPUs including (but not limited) to MI50, MI60, MI100, and MI200. Future versions on ROCm-SMI are expected to be backward compatible, and upcoming AMD GPU hardware for El Capitan supercomputer is expected to be supported through ROCm-SMI as well.

#### Monitoring and Control Through E-SMI API

Variorum interfaces with AMD's E-SMI library for obtaining power and energy information. These E-SMI APIs are described below.

The built-in monitoring interface on the AMD EPYC<sup>™</sup> processors is implemented by the SMU FW. All registers are updated every 1 millisecond.

#### **Power telemetry**

- esmi\_socket\_power\_get(): Instantaneous power is reported in milliwatts

- esmi\_socket\_power\_cap\_get() and esmi\_socket\_power\_cap\_set(): Get and Set power limit of the socket in milliwatts

- esmi\_socket\_power\_cap\_max\_get(): Maximum Power limit of the socket in milliwatts

#### **Boostlimit telemetry**

Boostlimit is a maximum frequency a CPU can run at.

- esmi\_core\_boostlimit\_get() and esmi\_core\_boostlimit\_set(): Get and set the current boostlimit for a given core

- esmi\_socket\_boostlimit\_set(): Set boostlimit for all the cores in the socket

#### **Energy telemetry**

- esmi\_socket\_energy\_get(): Get software accumulated 64-bit energy counter for a given socket

- esmi\_core\_energy\_get(): Get software accumulated 64-bit energy counter for a given core

Details of the AMD E-SMS CPU stack can be found on the AMD Developer website. We reproduce a figure from this stack below.

#### Monitoring and Control Through ROCM-SMI API

Variorum interfaces with AMD's ROCm-SMI library for obtaining power and energy information for GPUs. These ROCm-SMI APIs are described below.

- rsmi\_num\_monitor\_devices: Get the number of GPU devices.

- rsmi\_dev\_power\_ave\_get: Get the current average power consumption of a GPU device over a short time window in microwatts.

- rsmi\_dev\_power\_cap\_get: Get the current power cap in microwatts on a GPU device which, when reached, causes the system to take action to reduce power.

- rsmi\_dev\_power\_cap\_range\_get: Get the range of valid values for the power cap, including the maximum possible and the minimum possible cap on a GPU device.

- rsmi\_dev\_temp\_metric\_get: Get the temperature metric value for the specified metric and sensor (e.g. Current or Max temperature), from the GPU device.

- rsmi\_dev\_gpu\_clk\_freq\_get: Get the list of possible system clock speeds for a GPU device for a specified clock type (e.g. Graphics or Memory clock).

- rsmi\_utilization\_count\_get: Get coarse grain utilization counter of the specified GPU device, including graphics and memory activity counters.

- rsmi\_dev\_power\_cap\_set: Set the GPU device power cap for the specified GPU device in microwatts.

#### References

- AMD EPYC processors Fam19h technical reference

- AMD ROCm-SMI technical reference

### 5.6.2 ARM Overview

Variorum supports two flavors of ARM architectures: - Arm Juno r2 SoC - Ampere Neoverse N1

The Arm Juno r2 platform is a big.LITTLE cluster with Cortex-A72 (big) and Cortex-A53 (LITTLE) clusters (also called processors), respectively. It also has an Arm Mali GP-GPU. We have tested the ARM functionality of Variorum on Linaro supported Linux.

The Ampere Neoverse N1 platform is an 80-core single-processor platform with two Nvidia Ampere GPUs.

#### **Requirements**

This version of the ARM port of Variorum depends on the Linux Hardware Monitoring (hwmon) subsystem for access to the telemetry and control interfaces on the tested ARM platform. The standardized data interfaces provided by the hwmon framework enable a generic ARM implementation of Variorum.

#### **Model Identification**

Variorum use the *MIDR\_EL1* (Main ID) register which provides the identification information of the ARM processor to initialize the low-level interfaces on the target architecture. Specifically, Variorum uses bits [15:4] of *MIDR\_E1* to get the primary part number. For Neoverse N1 the primary part number is 0xD0C whereas for Arm Juno r2 big.LITTLE SoC the primary part numbers are 0xD08 (Cortex-A72) and 0xD03 (Cortex-A53).

#### Monitoring and Control Through Sysfs Interface

The built-in monitoring interface on the Arm Juno r2 board is implemented by the on-board FPGA. Since this interface is not universally available on most Arm implementations, we leverage the standard Linux sysfs interface for monitoring and control. The following subsections provide the specific metrics that are monitored on Arm Juno r2:

#### **Power telemetry**

The sysfs interface provides a file for each of the following Advanced Peripheral Bus (APB) energy meter registers:

- SYS\_POW\_SYS:/sys/class/hwmon/hwmon0/power1\_input

- SYS\_POW\_A72:/sys/class/hwmon/hwmon0/power2\_input

- SYS\_POW\_A53:/sys/class/hwmon/hwmon0/power3\_input

- SYS\_POW\_GPU:/sys/class/hwmon/hwmon0/power4\_input

Instantaneous power is recorded in bits 0-23 and reported in microwatts by the sysfs interface. To improve readability of the verbose output Variorum converts power into milliwatts before reporting. All registers are updated every 100 microseconds.

Memory power telemetry is not available on this platform.

#### **Thermal telemetry**

The sysfs interface provides a file for thermal telemetry for each system component through the GetSensorValue command in CSS System Control and Power Interface (SCPI).

- SoC temperature: /sys/class/hwmon/hwmon0/temp1\_input

- big temperature: /sys/class/hwmon/hwmon0/temp2\_input

- LITTLE temperature: /sys/class/hwmon/hwmon0/temp3\_input

- GPU temperature: /sys/class/hwmon/hwmon0/temp4\_input

Instantaneous temperatures are reported in degree Celsius.

On the Neoverse N1 system, the following thermal sensors are provided:

- Ethernet connector temperature: /sys/class/hwmon/hwmon0/temp1\_input

- SoC temperature: /sys/class/hwmon/hwmon1/temp1\_input

#### **Clocks telemetry**

Clocks are collected by the sysfs interface using the GetClockValue command in SCPI on both of the supported ARM platforms. On the Arm Juno r2 platform, a separate policy\*/ subdirectory is provided for the big and LITTLE clusters.

- big clocks: /sys/devices/system/cpu/cpufreq/policy0/scaling\_cur\_freq

- LITTLE clocks: /sys/devices/system/cpu/cpufreq/policy1/scaling\_cur\_freq

On the Neoverse N1 platform, a separate policy\*/ subdirectory is provided for each core in the SoC.

• Core clocks: /sys/devices/system/cpu/cpufreq/policy[0-79]/scaling\_cur\_freq

Frequencies are reported by the sysfs interface in KHz. Variorum reports the clocks in MHz to keep it consistent with the clocks reported for other supported architectures.

#### **Frequency control**

The sysfs interface uses the SetClockValue SCPI command to set processor frequency for the following user-facing interfaces on the supported platforms:

Arm Juno r2:

- big clocks: /sys/devices/system/cpu/cpufreq/policy0/scaling\_setspeed

- LITTLE clocks: /sys/devices/system/cpu/cpufreq/policy1/scaling\_setspeed

Neoverse N1:

• core clocks: /sys/devices/system/cpu/cpufreq/policy[0-79]/scaling\_setspeed

New frequency is specified in KHz to these interfaces. Variorum takes the new frequency as input in MHz and performs this conversion internally.

If you run into an error accessing the sysfs interface, this could be due to an the specified frequency value or the set governor. The sysfs interface only accepts valid values for frequencies as output by policy\*/ scaling\_available\_frequencies. Also, the specified frequency is only applied when the governor in policy\*/ scaling\_governor is set to *userspace*.

#### References

- Arm Juno r2 technical reference

- Neoverse N1 technical reference

- Cortex-A53 technical reference

- Cortex-A72 technical reference

- hwmon sysfs interface

- hwmon documentation

- Energy Monitoring on Juno

#### 5.6.3 IBM Power9 Overview

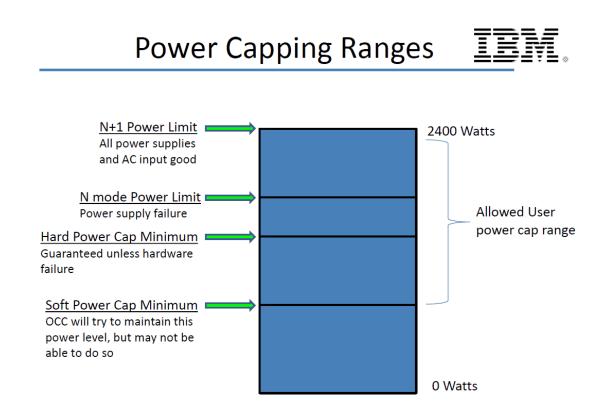

IBM Power9 architecture supports in band monitoring with sensors and out of band power capping with OPAL. These depend on specific IBM files that we describe below. Permissions on these files can be modified through cgroups. OPAL/Skiboot is part of IBM provided firmware that is expected to be present on the system.

#### **Requirements**

Read access to /sys/firmware/opal/exports/occ\_inband\_sensors is required, along with read-write access to /sys/firmware/opal/powercap/system\_powercap/powercap\_current and /sys/firmware/opal/psr/. This can be enabled by using group permissions. For example, to allow only users belonging to certain group to set the power cap or power shifting ratio, udev can be used as follows.

```

$ cat /etc/udev/rules.d/99-coral.rules

KERNELS=="*", ACTION=="*", DEVPATH=="/devices/*", RUN+="/bin/chown root:coral

/sys/firmware/opal/powercap/system-powercap/powercap-current

/sys/firmware/opal/psr/cpu_to_gpu_0

/sys/firmware/opal/psr/cpu_to_gpu_8"

```

The above file needs to be copied to all nodes. The administrator has to create a group (for example, named coral below) and add the users to this group. The udev rule can then be set as follows:

```

$ udevadm trigger /sys/block/sda

```

```

$ ls -l /sys/firmware/opal/powercap/system-powercap/powercap-current \

/sys/firmware/opal/psr/cpu_to_gpu_0 /sys/firmware/opal/psr/cpu_to_gpu_8

-rw-rw-r- 1 root coral 65536 Jul 3 06:19 /sys/firmware/opal/powercap/system-powercap/

-powercap-current

-rw-rw-r- 1 root coral 65536 Jul 3 06:19 /sys/firmware/opal/psr/cpu_to_gpu_0

-rw-rw-r- 1 root coral 65536 Jul 3 06:19 /sys/firmware/opal/psr/cpu_to_gpu_8

```

#### **Inband Sensors for Monitoring**

The OCC (On-Chip-Controller) periodically reads various sensors related to power, temperature, CPU frequency, CPU utilization, memory bandwidth, etc. The sensor data is stored in OCC's SRAM and is available to the user inband through the sensors file listed below:

• Key file for inband sensors: /sys/firmware/opal/exports/occ\_inband\_sensors

OCC Sensor Data formatting is described below, and we then describe the code structures that were used to represent this data in the IBM port of Variorum.

#### **OCC Sensor Data**

OCC sensor data will use BAR2 (OCC Common is per physical drawer). Starting address is at offset 0x00580000 from BAR2 base address. Maximum size is 1.5MB.

| Start (Offset from BAR2 base address) | End        | Size  | Description             |

|---------------------------------------|------------|-------|-------------------------|

| 0x00580000                            | 0x005A57FF | 150kB | OCC 0 Sensor Data Block |

| 0x005A5800                            | 0x005CAFFF | 150kB | OCC 1 Sensor Data Block |

| :                                     | :          | :     | :                       |

| 0x00686800                            | 0x006ABFFF | 150kB | OCC 7 Sensor Data Block |

| 0x006AC000                            | 0x006FFFFF | 336kB | Reserved                |

#### OCC N Sensor Data Block Layout (150kB)

The sensor data block layout is the same for each OCC N. It contains sensor-header-block, sensor-names buffer, sensor-readings-ping buffer and sensor-readings-pong buffer.

| Start (Offset from OCC N Sensor Data Block) | End        | Size | Description                 |

|---------------------------------------------|------------|------|-----------------------------|

| 0x0000000                                   | 0x000003FF | 1kB  | Sensor Data Header Block    |

| 0x00000400                                  | 0x0000CBFF | 50kB | Sensor Names                |

| 0x0000CC00                                  | 0x0000DBFF | 4kB  | Reserved                    |

| 0x0000DC00                                  | 0x00017BFF | 40kB | Sensor Readings ping buffer |

| 0x00017C00                                  | 0x00018BFF | 4kB  | Reserved                    |

| 0x00018C00                                  | 0x00022BFF | 40kB | Sensor Readings pong buffer |

| 0x00022C00                                  | 0x000257FF | 11kB | Reserved                    |

There are eight OCC Sensor Data Blocks. Each of these has the same data block layout. Within each sensor data block, we have:

- data header block: Written once at initialization, captured in occ\_sensor\_data\_header struct (reading\_version in this struct defines the format of the ping/pong buffer, this could be READING\_FULL or READ-ING\_COUNTER).

- names block: Written once at initialization, captured in occ\_sensors\_name

- **readings ping buffer and readings pong buffer**: The ping/pong buffers are two 40kB buffers, one is being updated by the OCC and the other is available for reading. Both have the same format version (defined in sensor\_struct\_type and struct\_attr).

There are four enums:

1. occ\_sensor\_type: e.g., CURRENT, VOLTAGE, TEMPERATURE, POWER, etc.

- 2. occ\_sensor\_location: e.g., SYSTEM, PROCESSOR, MEMORY, CORE, etc.

- 3. sensor\_struct\_type: READING\_FULL, READING\_COUNTER (ties to reading\_version)

- 4. sensor\_attr: SAMPLE, ACCUMULATOR (also has to do with reading\_version)

There are four structs:

- 1. **occ\_sensor\_data\_header**: Gives us offsets to ping and pong buffers, format version of the ping and pong buffers (reading\_version), and offset to location of the names buffer.

- 2. **occ\_sensor\_name**: Format of the sensor. Gives us the type of sensor, location of sensor, name of sensor, unit of sensor, update frequency of sensor, format of ping/pong buffer of that particular sensor, offset for reading buffers for this particular sensor.

- 3. **occ\_sensor\_record**: This is the data if you were using READING\_FULL. Contains timestamp, latest sample or latest accumulated value, min and max values for sample, job scheduler, profiler and CSM (we're not clear about what these are). We think the sample one is the interesting one for our purpose at the moment.

- 4. **occ\_sensor\_counter**: This is the data if you were using READING\_COUNTER. Contains timestamp, latest sample or latest accumulated value. unit\_8 values and no min/max values are reported here.

#### Inband Power Capping and GPU Shifting Ratio

Power caps and GPU power shifting ratio can be set by using OPAL/Skiboot. This is an inband interface through the BMC located on the node.

Node power caps are set by writing to the following file in Watts: /sys/firmware/opal/powercap/ system-powercap/powercap-current

Socket level power capping and memory power capping is not available.

GPU power shifting ratio can be set by setting the following files in percentage (i.e., between 0 and 100). /sys/firmware/opal/psr/cpu\_to\_gpu\_0 and /sys/firmware/opal/psr/cpu\_to\_gpu\_8

Write access to these files is needed to set node power caps and GPU ratio.

The figure below depicts the ranges for IBM power caps on Power9 system (reproduced with permission from our IBM collaborators).

The figure below shows the details of GPU power shifting ratio.

#### References

- OCC

- OPAL

- Skiboot

- Inband Sensors

### 5.6.4 Intel Overview

Intel processors have the most sophisticated power and thermal control of any processor vendor we work with. While Intel's documentation remains the final arbiter, that format has not allowed the community of Intel users to discuss best practices and distribute documentation patches. For this release we provide below a listing of the MSRs found in Chapter 14 of volume 3B of Intel's SDM, plus a few related MSRs that exist elsewhere in public documentation. Alongside the register diagrams we note what we have learned (if anything) by using the registers and discussing them with our colleagues at Intel and elsewhere.

#### **Requirements**

To use Variorum on Intel platforms, access to low-level registers needs to be enabled for non-root users. This can be enabled with the msr-safe kernel driver which must be loaded to enable user-level read and write of allowed MSRs.

The msr-safe driver provides the following device files:

/dev/cpu/<CPU>/msr\_safe

Alternately, Variorum can be used as root with the stock MSR kernel driver loaded.

modprobe msr

The kernel driver provides an interface to read and write MSRs on an x86 processor.

The stock MSR driver provides the following device files:

ls /dev/cpu/<CPU>/msr

#### **Best Practices**

These are the most common mistakes we have seen when using these registers.

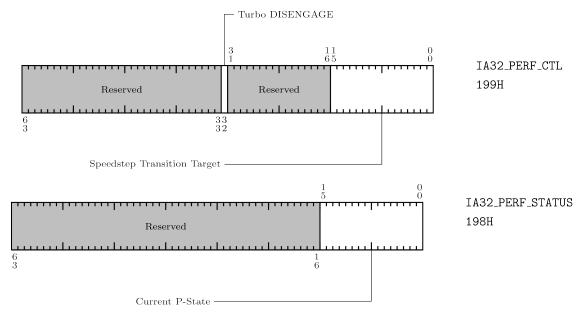

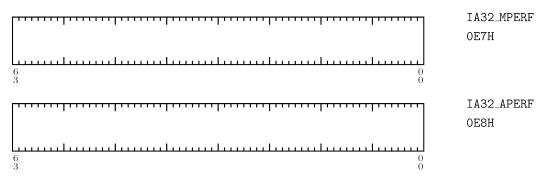

#### • IA32\_PERF\_CTL does not set clock frequency

- In the distant past prior to multicore and turbo, setting IA32\_PERF\_CTL might have had the effect

of dialing in the requested CPU clock frequency. In any processor since Nehalem, however, it sets a

frequency cap.

- Always measure effective clock frequency using IA32\_APERF and IA32\_MPERF.

- Given the amount of performance variation within the operating system and within and across processors, it is easy to talk oneself into a story of how a particular dial relates to performance by changing the clock frequency. Measuring both execution time and clock frequency (and perhaps IPC as well) is an excellent filter for those stories.

- Do not use Linux performance governors as they have limited support.

- Not all encodable values are effective.

- The canonical case here is RAPL time windows. There is a minimum value supported in firmware, and any request for less than that minimum is silently clipped.

#### Caveats

- Intel naming conventions are often inconsistent.

- Naming conventions will vary across and within documents, even to the naming of particular MSRs. While these are trivial to the eye (CTL versus CONTROL, PKG versus PACKAGE) it does make grepping documents more challenging than it should be. We have tried to follow a consistent scheme for MSRs, PCI addresses and CPUID queries. Where there is a conflict in MSR names, we have chosen what seems most sensible.

- Determining which MSRs are available on which processors is problematic.

- Motherboard manufacturers can mask out available MSRs, and Intel's documentation can contain errors.

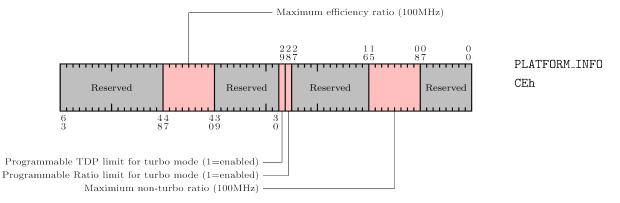

#### **Enhanced Intel Speedstep Technology**

- Exists if CPUID.(EAX=1):ECX[7] == 1.

- Enabled by IA32\_MISC\_ENABLE[16] <- 1.

- MSRs used:

- IA32\_PERF\_CTL

- IA32\_PERF\_STATUS

- IA32\_PM\_ENABLE

- MSR\_PLATFORM\_INFO

• IA32\_PM\_ENABLE will disable IA32\_PERF\_CTL. The enable bit is sticky and requires a reset to clear.

• MSR\_PLATFORM\_INFO Maximum Efficiency Ratio is the only guaranteed frequency regardless of workload.

# **P-State Hardware Coordination**

- Exists if CPUID.(EAX=6):ECX[0] == 1

- MSRs used:

- IA32\_MPERF

- IA32\_APERF

# Intel Dynamic Acceleration Technology/Intel Turbo Boost Technology

- Enabled by MSR\_MISC\_ENABLE[38] <- 1, IA32\_PERF\_CTL[32] <- 0

- Note that the former is intended for one-time use by BIOS, the latter is intended for dynamic control.

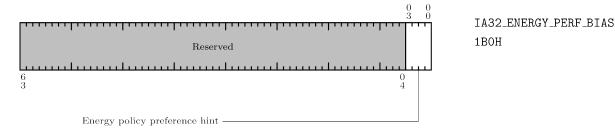

# Performance and Energy Bias Hint Support

- Exists if CPUID.(EAX=6):ECX[3] == 1

- MSRs used:

- IA32\_ENERGY\_PERF\_BIAS

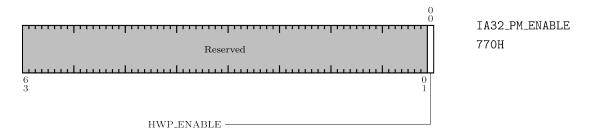

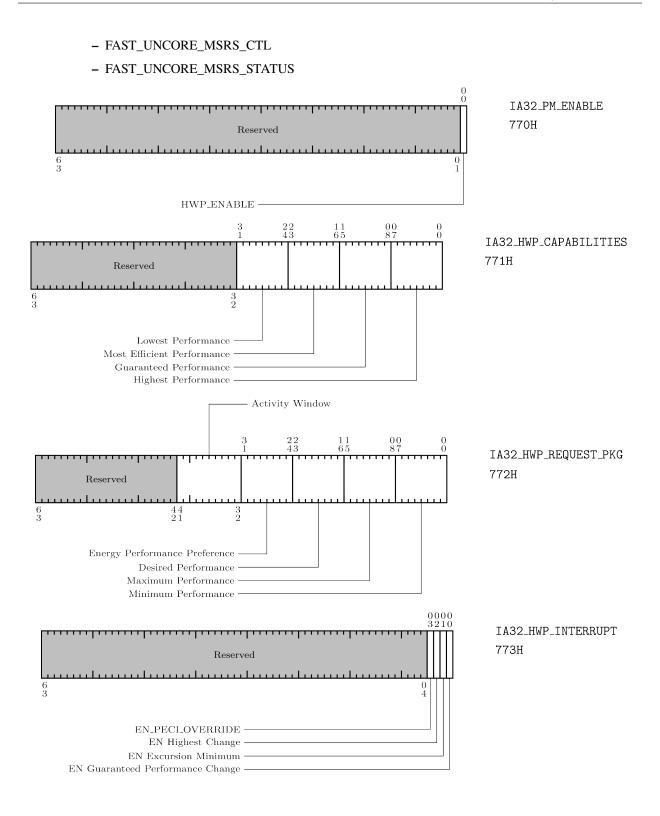

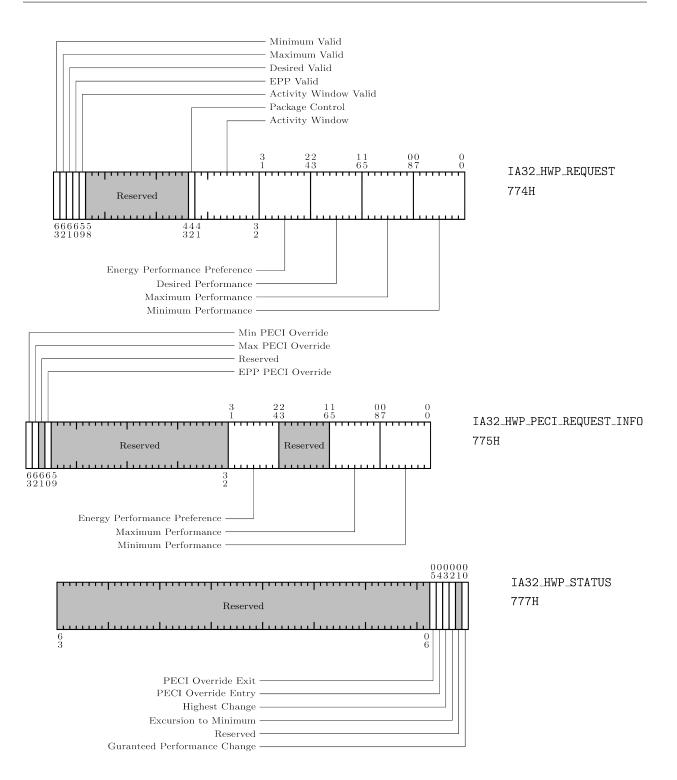

# Hardware Controlled Performance States

- If CPUID.(EAX=6):EAX[7] == 1, then IA32\_PM\_ENABLE, IA32\_HWP\_CAPABILITIES, IA32\_HWP\_REQUEST, IA32\_HWP\_STATUS present.

- If CPUID.(EAX=6):EAX[8] == 1, then IA32\_HWP\_INTERRUPT present.

- If CPUID.(EAX=6):EAX[9] == 1, then IA32\_HWP\_REQUEST contains a programmable activity window.

- If CPUID.(EAX=6):EAX[10]== 1, then IA32\_HWP\_REQUEST has a programmable energy/performance hint.

- If CPUID.(EAX=6):EAX[11]== 1, then IA32\_HWP\_REQUEST\_PKG is present.

- If CPUID.(EAX=6):EAX[20]== 1 and a single logical processor of a core is active, requests originating in the idle virtual processor via IA32\_HWP\_REQUEST\_MSR are ignored.

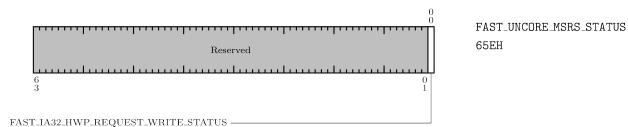

- If CPUID.(EAX=6):EAX[18]== 1, IA32\_HWP\_REQUEST writes become visible outside the originating logical processor via "fast writes."

- MSRs used:

- IA32\_PM\_ENABLE

- IA32\_HWP\_CAPABILITIES

- IA32\_HWP\_REQUEST\_PKG

- IA32\_HWP\_INTERRUPT

- IA32\_HWP\_REQUEST

- IA32\_HWP\_PECI\_REQUEST\_INFO

- IA32\_HWP\_STATUS

- IA32\_THERM\_STATUS

- MSR\_PPERF

- FAST\_UNCORE\_MSRS\_CAPABILITY

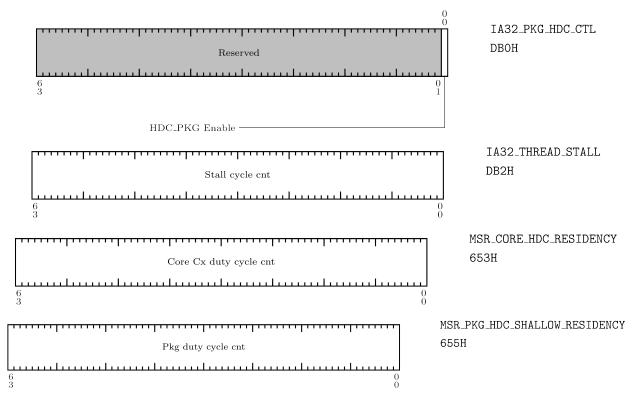

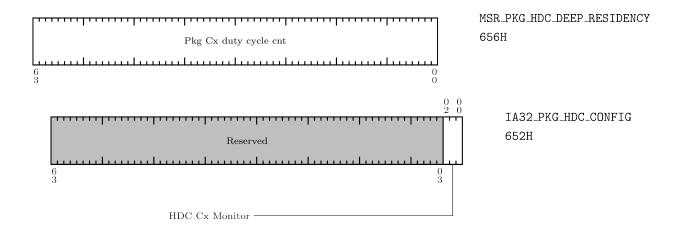

# Hardware Duty Cycling

- Present if CPUID.(EAX=6):EAX[13] == 1

- MSRs used:

- IA32\_PKG\_HDC\_CTL

- IA32\_PM\_CTL1

- IA32\_THREAD\_STALL

- MSR\_CORE\_HDC\_RESIDENCY

- MSR\_PKG\_HDC\_SHALLOW\_RESIDENCY

- MSR\_PKG\_HDC\_DEEP\_RESIDENCY

- MSR\_PKG\_HDC\_CONFIG

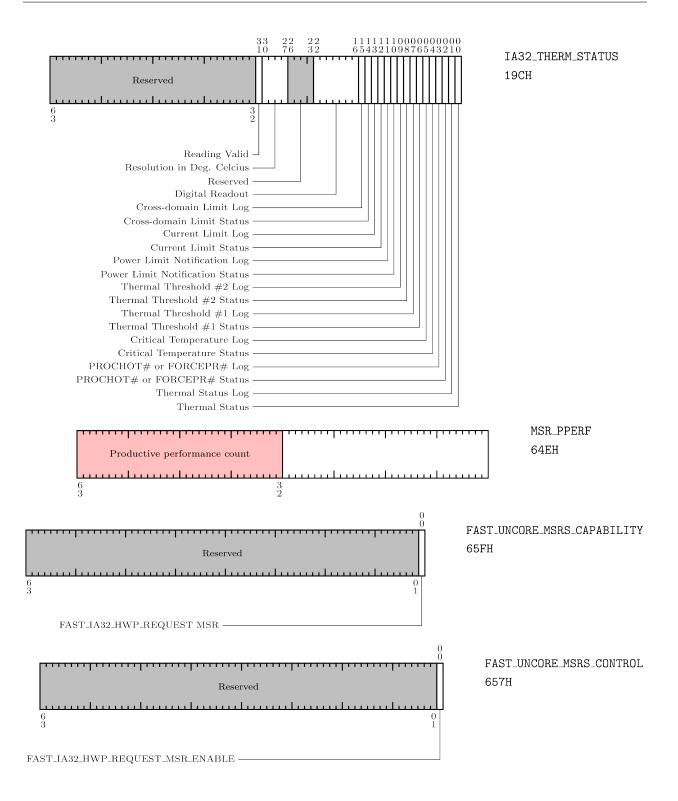

# **Thermal Monitoring and Protection**

- TM1 present if CPUID.(EAX=1):EDX[29] == 1, enabled by IA32\_MISC\_ENABLE[3]

- TM2 present if CPUID.(EAX=1):ECX[8] == 1, enabled by IA32\_MISC\_ENABLE[13]

- Digital Thermal Sensor Enumeration present if CPUID.(EAX=0):EAX[0]=1

- MSRs used

- MSR\_THERM2\_CTL

- IA32\_THERM\_STATUS

- IA32\_THERM\_INTERRUPT

- IA32\_CLOCK\_MODULATION

- IA32\_THERM\_STATUS

MSR\_THERM2\_CTL NOT AVAILABLE

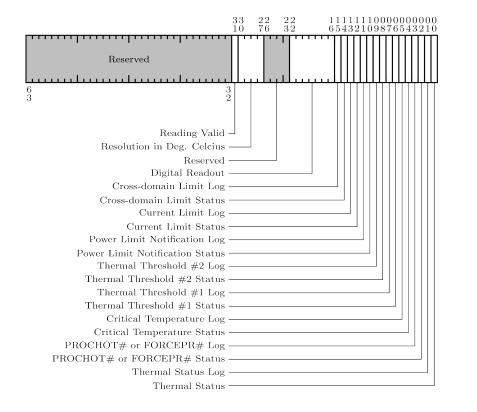

IA32\_THERM\_STATUS 19CH

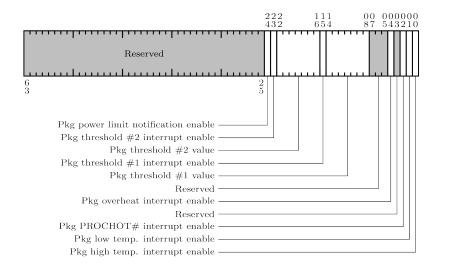

# Package Level Thermal Management

- Present if CPUID.(EAX=6):EAX[6] == 1

- MSRs used

- IA32\_PACKAGE\_THERM\_STATUS

- IA32\_PACKAGE\_THERM\_INTERRUPT

IA32\_PACKAGE\_THERM\_STATUS 1B1H

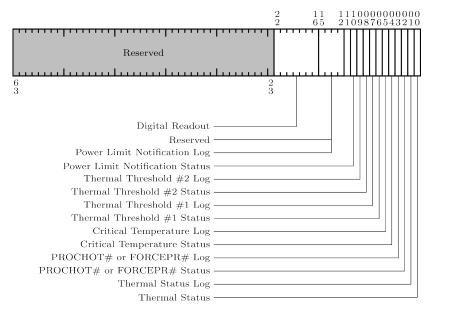

IA32\_PACKAGE\_THERM\_INTERRUPT 1B2H

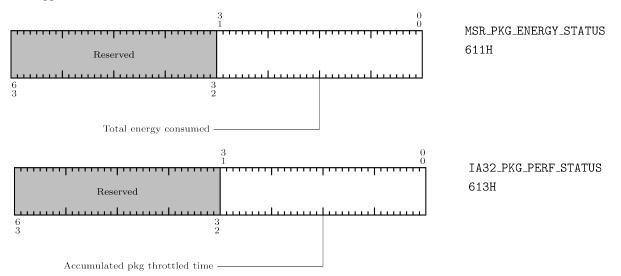

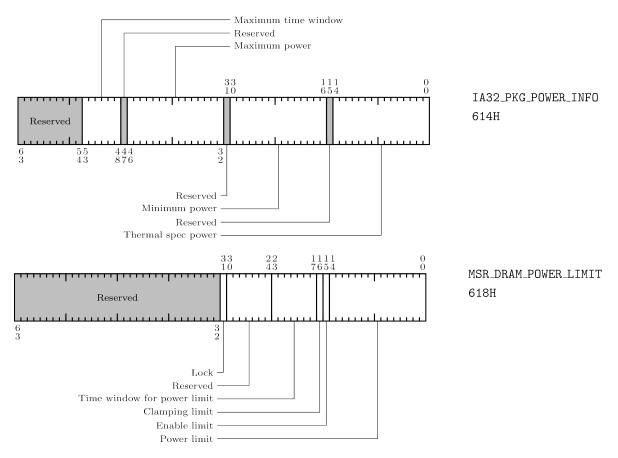

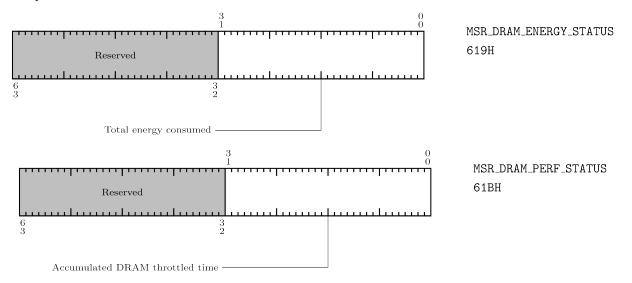

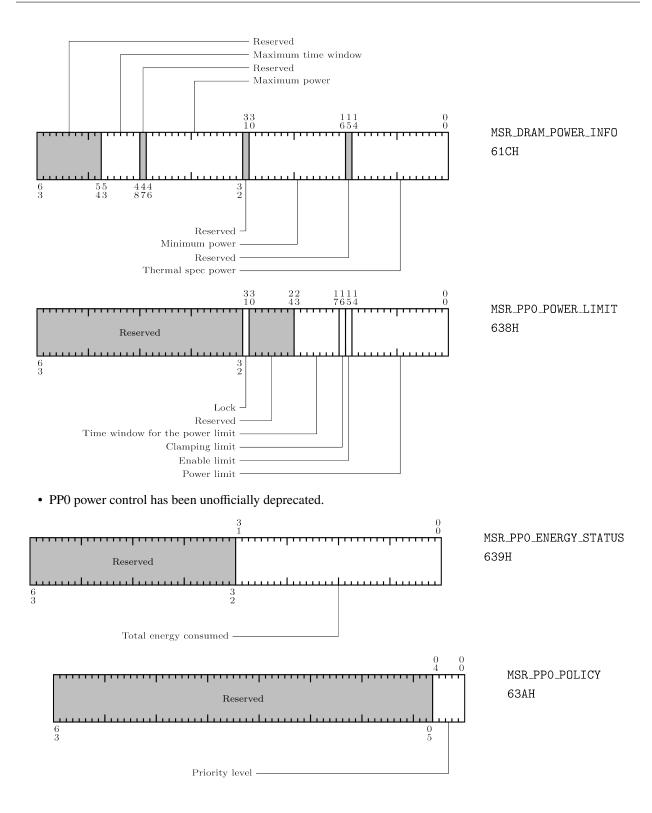

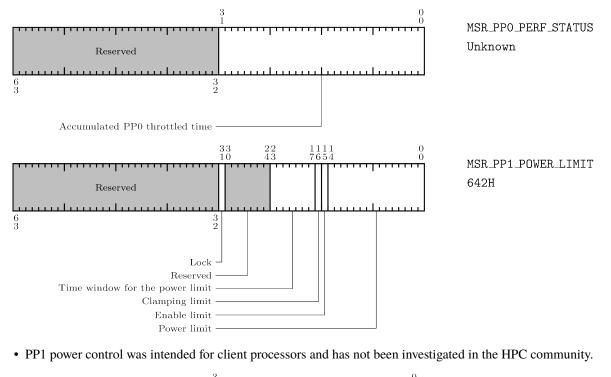

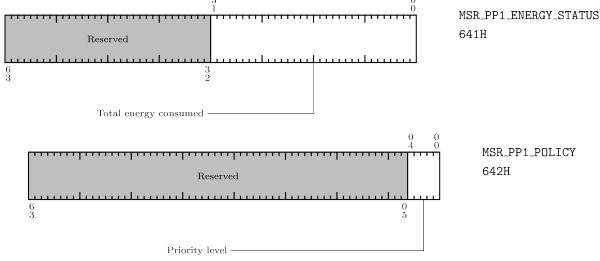

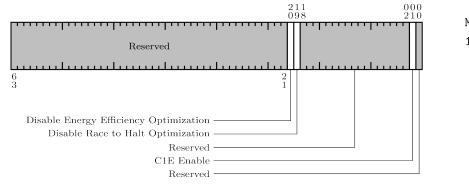

# **Platform Specific Power Management Support**

- MSRs used

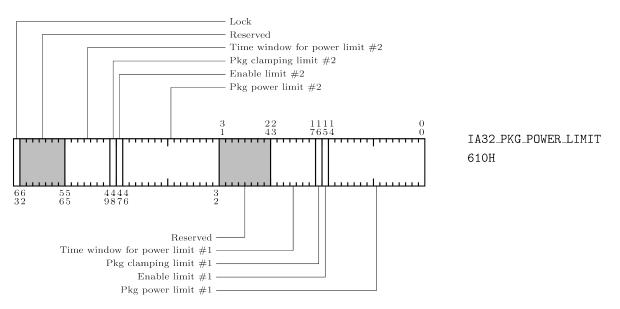

- MSR\_PKG\_POWER\_LIMIT

- MSR\_PKG\_ENERGY\_STATUS

- MSR\_PKG\_PERF\_STATUS

- MSR\_PKG\_POWER\_INFO

- MSR\_DRAM\_POWER\_LIMIT

- MSR\_DRAM\_ENERGY\_STATUS

- MSR\_DRAM\_PERF\_STATUS

- MSR\_DRAM\_POWER\_INFO

- MSR\_PP0\_POWER\_LIMIT

- MSR\_PP0\_ENERGY\_STATUS

- MSR\_PP0\_POLICY

- MSR\_PP0\_PERF\_STATUS

- MSR\_PP1\_POWER\_LIMIT

- MSR\_PP1\_ENERGY\_STATUS

- MSR\_PP1\_POLICY

- The two different power limits use different algorithms and are intended for use across different timescales. The details are still NDA.

- There is a lower limit to the time windows. Values below that will be silently clipped. That value is also NDA.

- The OS and enable bits are now ignored. Both of them should always be set high. Writing all-zeros to this register will not disable RAPL; the processor will just try to meet a zero-watt power bound (or whatever zero is clipped to).

• The DRAM power controls have not proven to be that useful. If a program is not generating much memory traffic, not much power is used. Programs that do generate lots of memory traffic have outsized slowdown if memory power is restricted.

# **Other Public MSRs of Interest**

• MSR\_POWER\_CTL

MSR\_POWER\_CTL 1FCH

# References

• Intel Software Developer Manuals

# 5.6.5 Intel Discrete GPUs Overview

This page provides a detailed description of the Intel Discrete GPU port of Variorum. The functionality of this port depends on Intel-specific proprietary software stack as well as open-source software components described below. The high-level API provided by Variorum is currently read-only (i.e., monitoring-only), primarily because of the access limitations on our target platform.

# Requirements

The Intel Discrete GPU port of Variorum depends on:

- APMIDG 0.3.0 or later

- One API 2022.06.30.002 or later

We have tested our port with Aurora early access systems with Intel ATS GPUs.

Note: at this point, monitoring power of Intel Discrete GPU requires no additional permission. However, the permission default setting may change in a future driver release. Please consult your sysadmin.

# **Build Configuration**

At this point, Intel GPUs are only available through an early evaluation system; thus, we recommend you request your account via https://www.jlse.anl.gov/ and request access to the Aurora early access systems (EAS). Once you gain access to EAS, type the following command to load compilers and the libraries required to build the Intel GPU port.

\$ module load cmake oneapi apmidg jansson hwloc libiconv

We provide an example CMake host config file, which defines the CMake build variables set on our test platform (Aurora early access supercomputer at ANL): arcticus-apmidg-oneapi.cmake.

If you want to build variorum on other systems besides JLSE nodes, please install all compiler and library dependencies, and then you will need to enable Variorum to build with INTEL\_GPU and set three path variables as described below:

- VARIORUM\_WITH\_INTEL\_GPU=ON

- APMDIG\_DIR: Path to libapmidg.so (prefixed with the '-L' flag)

- HWLOC\_DIR: Path to libhwloc.so

- JANSSON\_DIR: Path to libjansson.so

# **Device Enumeration**

The Intel GPU port enumerates the system GPU devices at initialization in the initAPMIDG() method, which internally obtains the number of Intel GPU devices via apmidg\_getndevs(). The number of GPUs per socket is simply the number of available GPUs divided by the number of CPU sockets returned by variorum\_get\_topology().

# **Telemetry Collection Through APMIDG Query Interface**

The Intel GPU port of Variorum leverages the device and unit query APIs provided by APMIDG to collect per-GPU telemetry or subdomain telemetry if available. The text below describes the specific Variorum APIs, the corresponding APMIDG APIs, and the post-processing (if any) performed by Variorum before presenting the data to the caller.

# **Power telemetry**

Variorum provides two APIs for power telemetry from the GPU devices:

• Average power usage

To report the average power usage of a GPU device, Variorum leverages the apmidg\_readpoweravg() API of AP-MIDG. The reported power is in Watts as a floating point number.

# **Thermal telemetry**

Variorum provides an API to report instantaneous GPU device temperature in degree Celsius and integer precision. It leverages the apmidg\_readtemp() APMIDG API to report the GPU device temperature in Celsius.

# **Clocks telemetry**

Variorum provides an API to report instantaneous clock speed of the Intel GPU's execusion unit in MHz and integer precision. It leverages the apmidg\_readfreq() APMIDG API to report the instantaneous clock speed.

# **Control Interface**

The Intel Discrete GPU port of Variorum leverages the device-level control APIs provided by APMIDG. Variorum implements the following device control APIs using the corresponding APMIDG APIs.

# **Power control**

In Variorum's GPU power capping API, Variorum uses the apmidg\_setpwrlim() API of APMIDG which takes as input the GPU device ID, the power domain ID and the power cap in milliwatts.

## References

• APMDIG library

# 5.6.6 NVIDIA Overview

This page provides a detailed description of the the NVIDIA port of Variorum. The functionality of this port depends on NVIDIA-specific proprietary software stack as well as open-source software components described below. The high-level API provided by Variorum is read-only (i.e., monitoring-only), primarily because of the access limitations on our target platform.

# **Requirements**

The NVIDIA port of Variorum depends on:

- NVIDIA Management Library (NVML) for access to the telemetry and control interfaces. NVML provides standardized interfaces to the NVIDIA GPU devices enumerated by the proprietary NVIDIA device driver as /dev/nvidia[0-9]\*.

- CUDA development toolkit, 10.1.243+ which delivers the headers for NVML.

- CUDA-enabled build of the Portable Hardware Locality (hwloc) library to enumerate the GPU devices and their mappings to the host CPUs. This requires hwloc to be built with the HWLOC\_HAVE\_CUDA flag.

To successfully use the Variorum port of NVIDIA, verify that the LD\_LIBRARY\_PATH environment variable has paths for both the CUDA library and the CUDA-enabled hwloc library installed on the system. Also make sure that access to the NVIDIA devices (/dev/nvidia\*) through the NVIDIA driver are set correctly for the user. This can be verified by running the *nvidia-smi* command line tool.

We have tested our NVIDIA port with CUDA 9.2 and CUDA-enabled build of hwloc 1.11.10. The NVIDIA port has been tested on the Tesla GPU architecture (NVIDIA Volta SM200).

# **Build Configuration**

We provide an example CMake host config file, which defines the CMake build variables set on our test platform (Lassen supercomputer at LLNL): *lassen-4.14.0-ppc64le-gcc@4.9.3-cuda@10.1.243.cmake*.

For your build system, you will need to enable Variorum to build with NVIDIA and set two path variables as described below:

- VARIORUM\_WITH\_NVIDIA\_GPU=ON

- CMAKE\_SHARED\_LINKER\_FLAGS: Path to libnvidia-ml.so (prefixed with the '-L' flag)

- HWLOC\_DIR: Path for the CUDA-aware version of libhwloc

# **Device Enumeration**

The NVIDIA port enumerates the system GPU devices and populates global GPU device handles at initialization in the initNVML() method using the nvmlDeviceGetCount() and nvmlDeviceGetHandleByIndex() NVML query APIs, respectively. It then queries the number of CPUs using Variorum's internal routine to query system topology which uses the CUDA-enabled hwloc. Based on this information, it calculates the number of GPU devices associated with each CPU assuming sequential device assignment on the system. This method also initializes the internal state of NVML using the nvmlInit() API.

The device handles are stored in data structures of type nvmlDevice\_t defined in NVML. A device handle provides the logical-to-physical mapping between the sequential device IDs and system device handles maintained by NVML internally at state initialization. All NVML query and command APIs require the device handles to perform the specified operation on the device. While the high-level Variorum APIs operate over all devices, the internal routines in the NVIDIA port use CPU ID to perform operations on the associated GPUs.

# **Telemetry Collection Through NVML Query Interface**

The NVIDIA port of Variorum leverages the device and unit query APIs provided by NVML to collect per-GPU telemetry. The text below describes the specific Variorum APIs, the corresponding NVML APIs, and the post-processing (if any) performed by Variorum before presenting the data to the caller.

# **Power telemetry**

Variorum provides two APIs for power telemetry from the GPU devices:

- Average power usage

- Current power limit

To report the average power usage of a GPU device, Variorum leverages the nvmlDeviceGetPowerUsage() API of NVML. The reported power is in Watts as an integer.

To report the power limit assigned to a GPU device, Variorum leverages the nvmlDeviceGetPowerManagementLimit() API of NVML. The reported power limit is in Watts as an integer.

# Thermal telemetry

Variorum provides an API to report instantaneous GPU device temperature in degree Celsius and integer precision. It leverages the nvmlDeviceGetTemperature() NVML API to report the GPU device temperature.

# **Clocks telemetry**

Variorum provides an API to report instantaneous Streaming Multi-processor (SM) clock speed in MHz and integer precision. It leverages the nvmlDeviceGetClock() NVML API to report the instantaneous SM clock speed.

## **Device utilization**

Variorum provides an API to report the instantaneous device utilization as a percentage of time (samples) for which the GPU was in use (i.e., GPU occupancy rate) in a fixed time window. It leverages the nvmlDeviceGetUtilizationRates() API of NVML to report the device utilization rate as a percentage in integer precision.

#### **Power capping**

Variorum provides an API to cap GPU device power. The API applies the power cap equally to all GPU devices on the system. It leverages the nvmlDeviceSetPowerManagementLimit() API of NVML to set the power cap to the device after converting the specified power cap into milliwatts. This API requires root/administrator privileges.

#### References

• NVML API Reference

# 5.7 Monitoring Binaries with Variorum

While the Variorum API allows for detailed critical path analysis of the power profile of user applications as well as for integration with system software such as Kokkos, Caliper, and Flux through code annotations, there are scenarios where such annotations are not possible. In order to support such scenarios, we provide the var\_monitor tool, which can monitor a binary externally with Variorum in a vendor-neutral manner. This tool can monitor an application externally without requiring any code changes or annotations.

The variorum/src/var\_monitor directory contains this tool, which is built along with the regular Variorum build. While a target executable is running, var\_monitor collects time samples of power usage, power limits, energy, thermals, and other performance counters for all sockets in a node at a regular interval. By default, it collects basic node-level power information, such as CPU, memory, and GPU power, at 50ms intervals, which it reports in a CSV format. It also supports a verbose (-v) mode, where additional registers and sensors are sampled for the advanced user. The sampling rate is configurable with the -i option. As an example, the command below will sample the power usage while executing a sleep for 10 seconds in a vendor neutral manner:

\$ var\_monitor -a "sleep 10"

The resulting data is written to two files:

```

hostname.var_monitor.dat

hostname.var_monitor.summary

```

Here, hostname will change based on the node where the monitoring is occurring. The summary file contains global information such as execution time. The dat file contains the time sampled data, such as power, thermals, and performance counters in a column-delimited format. The output differs on each platform based on available counters.

var\_monitor also supports profiling across multiple nodes with the help of resource manager commands (such as srun or jsrun) or MPI commands (such as mpirun). As shown in the example below, the user can specify the number of nodes through mpirun and utilize var\_monitor with their application.

\$ mpirun -np <num-nodes> ./var\_monitor -a ./application

We also provide a set of simple plotting scripts for var\_monitor, which are located in the src/var\_monitor/ scripts folder. The var\_monitor-plot.py script can generate per-node as well as aggregated (across multiple nodes) graphs for the default version of var\_monitor that provides node-level and CPU, GPU and memory data. This script works across all architectures that support Variorum's JSON API for collecting power. Additionally, for IBM sensors data, which can be obtained with the var\_monitor -v (verbose) option, we provide a post processing and R script for plots.

In addition to var\_monitor that is vendor-neutral, for Intel systems only, we provide two other power capping tools, power\_wrapper\_static, and power\_wrapper\_dynamic that allow users to set a static (or dynamic) power cap and then monitor their binary application.

The example below will set a package-level power limit of 100W on each socket, and then sample the power usage while executing a sleep for 10 seconds:

```

$ power_wrapper_static -w 100 -a "sleep 10"

```

Similarly, the example below will set an initial package-level power limit of 100W on each socket, sample the power usage, and then dynamically adjust the power cap step-wise every 500ms while executing a sleep for 10 seconds:

```

$ power_wrapper_dynamic -w 100 -a "sleep 10"

```

# 5.8 Variorum Utilities

Variorum provides some utilities to assist users and developers. Currently, Variorum provides two main utilities:

- verify\_opal.py: A python script to verify the system environment (i.e., OPAL) for IBM platforms.

- verify\_msr\_kernel.py: A python script to verify the system environment (i.e., msr kernel or msr-safe kernel) for Intel.

# 5.8.1 Verify OPAL

This python script verifies that the OPAL files are present and have the required R/W permissions on the target IBM hardware.

# How do I use it?

From the top-level Variorum directory:

(continues on next page)

(continued from previous page)

```

-- Check if /sys/firmware/opal/psr/cpu_to_gpu_8 is accessible by user: /sys/firmware/

→opal/psr/cpu_to_gpu_8 -- yes

-- Check if OPAL files are accessible by user

-- Check if OCC file is accessible by user: /sys/firmware/opal/exports/occ_inband_

→sensors -- ves

-- Check if powercap-current file is accessible by user: /sys/firmware/opal/powercap/

→system-powercap/powercap-current -- yes

-- Check if powercap-max file is accessible by user: /sys/firmware/opal/powercap/system-

→powercap/powercap-max -- yes

-- Check if powercap-min file is accessible by user: /sys/firmware/opal/powercap/system-

→powercap/powercap-min -- yes

-- Check if cpu_to_gpu0 file is accessible by user: /sys/firmware/opal/psr/cpu_to_gpu_0 -

→- ves

-- Check if cpu_to_gpu8 file is accessible by user: /sys/firmware/opal/psr/cpu_to_gpu_8 -

⊶- yes

-- Valid OPAL access

```

Invoke the script with python on the target IBM system. The -v flag enables verbose output, which can be helpful if your programs are running to permissions issues. The output of this script is helpful to send to the mailing list for debugging system issues.

The last line of the output will (verbose or not) will indicate if the IBM OPAL files exist and have the appropriate permissions.

## Why Do I Need This?

This is a helpful utility to run before launching any examples or tests, as it can verify that the required environment for Variorum is configured successfully.

# 5.8.2 Verify MSR Kernel

This utility will check if the stock msr kernel or the msr-safe kernel are loaded and configured correctly with the appropriate R/W permissions. It will first check if the msr kernel is loaded and has appropriate permissions. If this fails, then it will check if the msr-safe kernel is loaded and has appropriate permissions.

# How do I use it?

From the top-level Variorum directory:

(continues on next page)

(continued from previous page)

```

--- Check if msr_safe kernel files are character devices: /dev/cpu/71/msr_safe -- yes

-- Check if msr_safe kernel files are character devices: /dev/cpu/msr_allowlist -- yes

-- Check if msr_safe kernel files are character devices: /dev/cpu/msr_batch -- yes

-- Check if msr_safe kernel files are accessible by user

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/0/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/1/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/2/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/2/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/3/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/71/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/71/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/71/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/71/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/71/msr_safe -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/msr_allowlist -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/msr_allowlist -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/msr_allowlist -- yes

-- Check if msr_safe kernel files are accessible by user: /dev/cpu/msr_batch -- yes

-- Valid kernel loaded: msr-safe

```

Invoke the script with python on the target Intel system. The -v flag enables verbose output, which can be helpful if your programs are running to permissions issues. The output of this script is helpful to send to the mailing list for debugging system issues.

The last line of the output will (verbose or not) will indicate if the msr or msr-safe kernel is configured correctly and has the appropriate permissions.

# Why Do I Need This?

This is a helpful utility to run before launching any examples or tests, as it can verify that the required environment for Variorum is configured successfully.

# 5.9 Variorum Print Functions

Variorum provides the following high-level functions for printing the value of various features. For each feature, there is a print and print\_verbose API, which will print the metrics in different output formats. The print API prints the output in tabular format that can be filtered and parsed by a data analysis framework, such as R or Python. The print\_verbose API prints the output in verbose format that is more human-readable (with units, titles, etc.). See *Examples* for sample output formats supported by Variorum.

Defined in variorum/variorum.h.

#### int variorum\_print\_verbose\_energy(void)

Print verbose format of core and socket energy if available.

#### **Supported Architectures:**

- IBM Power9

- · Intel Sandy Bridge

- Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- · Intel Skylake

- · Intel Kaby Lake

- Intel Cascade Lake

- Intel Cooper Lake

#### Returns

0 if successful or if feature has not been implemented or is not supported, otherwise -1

#### int variorum\_print\_verbose\_power(void)

Print power usage data in long format.

# **Supported Architectures:**

- AMD EPYC Milan

- AMD Radeon Instinct GPUs (MI50 onwards)

- ARM Juno r2

- Ampere Neoverse N1

- IBM Power9

- · Intel Sandy Bridge

- Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- · Intel Skylake

- Intel Kaby Lake

- Intel Ice Lake

- Intel Cascade Lake

- · Intel Cooper Lake

- Intel Sapphire Rapids

- NVIDIA Volta

#### Returns

0 if successful or if feature has not been implemented or is not supported, otherwise -1

# int variorum\_print\_power(void)

Print power usage data in CSV format.

#### **Supported Architectures:**

- AMD EPYC Milan

- AMD Radeon Instinct GPUs (MI50 onwards)

- ARM Juno r2

- Ampere Neoverse N1

- IBM Power9

- Intel Sandy Bridge

- Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- Intel Skylake

- Intel Kaby Lake

- Intel Ice Lake

- Intel Cascade Lake

- Intel Cooper Lake

- Intel Sapphire Rapids

- Intel Arctic Sound

- NVIDIA Volta

#### Returns

0 if successful or if feature has not been implemented or is not supported, otherwise -1

# int variorum\_print\_verbose\_power\_limit(void)

Print power limits for all known domains in long format.

# **Supported Architectures:**

- AMD EPYC Milan

- AMD Radeon Instinct GPUs (MI50 onwards)

- IBM Power9

- Intel Sandy Bridge

- Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- Intel Skylake

- Intel Kaby Lake

- Intel Ice Lake

- Intel Cascade Lake

- · Intel Cooper Lake

- Intel Sapphire Rapids

- NVIDIA Volta

# Returns

### int variorum\_print\_power\_limit(void)

Print power limits for all known domains in CSV format.

# **Supported Architectures:**

- AMD EPYC Milan

- AMD Radeon Instinct GPUs (MI50 onwards)

- IBM Power9

- Intel Sandy Bridge

- Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- Intel Skylake

- Intel Kaby Lake

- Intel Ice Lake

- Intel Cascade Lake

- Intel Cooper Lake

- Intel Sapphire Rapids

- NVIDIA Volta

# Returns

0 if successful or if feature has not been implemented or is not supported, otherwise -1

# int variorum\_print\_verbose\_thermals(void)

Print thermal data in long format.

# **Supported Architectures:**

- AMD Radeon Instinct GPUs (MI50 onwards)

- ARM Juno r2

- Ampere Neoverse N1

- Intel Sandy Bridge

- Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- Intel Skylake

- Intel Kaby Lake

- Intel Cascade Lake

- Intel Cooper Lake

- NVIDIA Volta

#### Returns

0 if successful or if feature has not been implemented or is not supported, otherwise -1

### int variorum\_print\_thermals(void)

Print thermal data in CSV format.

## **Supported Architectures:**

- AMD Radeon Instinct GPUs (MI50 onwards)

- ARM Juno r2

- Ampere Neoverse N1

- Intel Sandy Bridge

- · Intel Ivy Bridge

- Intel Haswell

- Intel Broadwell

- Intel Skylake

- Intel Kaby Lake

- Intel Cascade Lake

- Intel Cooper Lake

- Intel Arctic Sound

- NVIDIA Volta

#### Returns